10.6 TLB测试

80386提供了一种机制来测试转换后备缓冲区(TLB),该缓冲区用来把线性地址转换成物理地址。尽管TLB硬件错误的机会非常小,但用户可能在上电信心测试的时候把TLB信心测试包含进来。

注意:

TLB测试机制是80386独有的,可能不会在将来的处理器中包含它。使用这种机制的软件可能会与将来的处理器不兼容。

当测试TLB的时候,建议您关闭页(CR0中的PG=0)以避免在正在写入TLB的数据引起冲突。

10.6.1 TLB结构

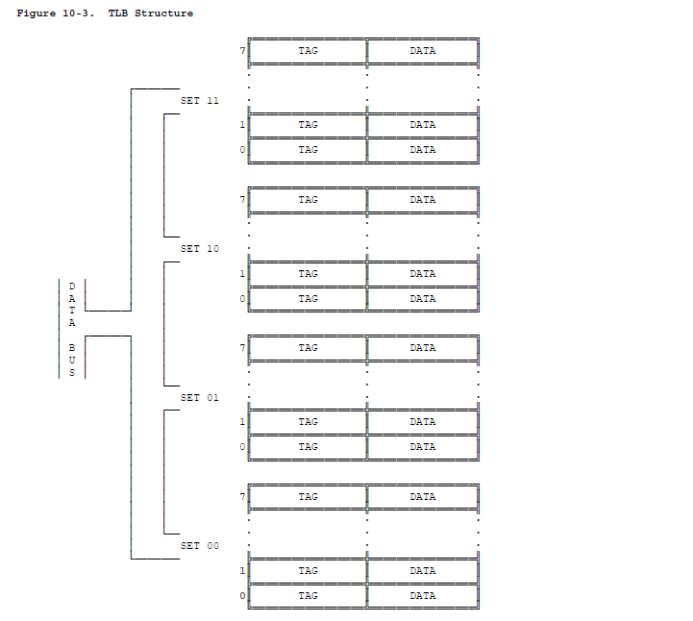

TLB是一个4路关联接收机。图10-3说明了TLB的结构。它有4个装置,每个包含8项。每项包含标签和数据。标签24位宽,它们包含高阶20位线性地址,检查位,以及3个属性位。数据域包含高阶20位物理地址。

10.6.2 测试寄存器

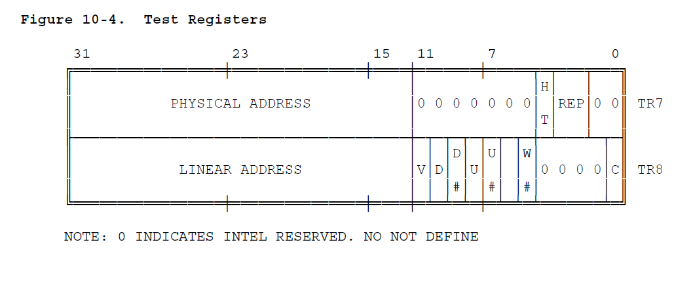

两个寄存器,如图10-4,用来测试。TR6是测试命令寄存器,TR7是测试数据寄存器。这些寄存器可以用MOV命令来访问。测试命令寄存器可以是源操作数,也可以是目的操作数。MOV在实地址模式和保护模式下都有定义。测试寄存器是特权资源;在保护模式下,只能在特权级0用MOV访问它们。在其他特权级的访问将导致通用保护异常。

测试命令寄存器(TR6)包含一个命令位和地址标签:

C

命令位。有两个TLB测试命令:向TLB写,和TLB检查。为了向TLB写数据,可以将双字用MOV写入TR6,并将该标志清零。为了TLB检查,可以将双字用MOV写入TR6,并且置位该标志位。

Linear Address

当执行TLB写后,一个TLB项被定位到这个线性地址;这个TLB项的其他部分由TR7和刚刚被写入的TR6来决定。当执行TLB检查时,通过这个值来审查TLB;如果有且仅有一项匹配,TR6和TR7的其他部分由该匹配项来设置。

V

TLB项的检查位。TLB用这项来检查TLB项是否含有合法数据。没有被分配数据的TLB项该标志位为零。所有的检查位可以通过写CR3来清除。

D, D#

脏标志(和它的补)来设置/读取TLB项。

U, U#

U/S标志(和它的补)来设置/读取TLB项。

W, W#

R/W标志(和它的补)来设置/读取TLB项。

这些标志对的含义见表10-1,X代表D, U, 或者W。

测试寄存器(TR7)用保存从TLB读取的数据,或要写入TLB的数据。

physical Address

TLB的数据域。当TLB写后,被分配给TR6中线性地址的TLB项被设置成这个值。当执行TLB检查时,如果设置了HT,TLB的数据域(物理地址)被读到这里。如果没有设置HT,该域未定义。

HT

对于TLB检查,HT决定检查被触发(HT<-1)或忽略(HT<-0)。对于TLB写,HT必须为1。

REP

对于TLB写,选择4个通道中的一个来写入。对于TLB读,如果设置了HT,REP报告出哪个通道找到了标签;如果没有设置HT,REP未定义。

Table 10-1. Meaning of D, U, and W Bit Pairs

X X# Effect during Value of bit X

TLB Lookup after TLB Write

0 0 (undefined) (undefined)

0 1 Match if X=0 Bit X becomes 0

1 0 Match if X=1 Bit X becomes 1

1 1 (undefined) (undefined)

10.6.3 测试操作

写TLB项:

1,向TR7中写入双字,包含需要的物理地址,HT,和REP值。HT必须为1。REP必须指向要放置该项的通道。 2,向TR6写入双字,包含合适的线性地址,以及V, D, U和W值。确保C=0。

要当心,不要写入重复的标签;这样做的结果未定义。

检查(读)TLB项:

1,向TR6写入双字,包含适当的线性地址和属性。确保C=1。 2,保存TR7。如果设置了HT,则其他值表示读到的TLB项的内容。如果没有设置HT,则其他值无法确定。

对于测试而言,V标志的作用类似于地址标志位。通常在检查的时候置位此标志位,使没有初始化的标签不参加匹配。如果不设置,则未初始化的标签会导致不可预料的结果。